# MIPS32 M4K<sup>TM</sup> Processor Core Software User's Manual

Document Number: MD00249 Revision 1.02 December 15, 2003

MIPS Technologies, Inc. 1225 Charleston Road Mountain View, CA 94043-1353

Copyright © 2000-2003 MIPS Technologies Inc. All rights reserved.

Copyright © 2000-2003 MIPS Technologies, Inc. All rights reserved.

Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.

This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying, reproducing, modifying or use of this information (in whole or in part) that is not expressly permitted in writing by MIPS Technologies or an authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.

Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS TECHNOLOGIES, INC.

MIPS Technologies reserves the right to change the information contained in this document to improve function, design or otherwise. MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Except as expressly provided in any written license agreement from MIPS Technologies or an authorized third party, the furnishing of this document does not give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

The information contained in this document shall not be exported, reexported, transferred, or released, directly or indirectly, in violation of the law of any country or international law, regulation, treaty, Executive Order, statute, amendments or supplements thereto. Should a conflict arise regarding the export, reexport, transfer, or release of the information contained in this document, the laws of the United States of America shall be the governing law.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or an authorized third party.

MIPS, MIPS16, QuickMIPS, R3000 and R5000 are among the registered trademarks of MIPS Technologies, Inc. in the United States and other countries, and MIPS16e, MIPS32, MIPS64, MIPS-3D, MIPS-Based, MIPS I, MIPS II, MIPS III, MIPS IV, MIPS V, MIPS RISC Certified Power logo, MIPSsim, MIPS Technologies logo, R4000, 4K, 4Kc, 4Km, 4Kp, 4KE, 4KEc, 4KEm, 4KEp, 4KS, 4KSc, 4KSd, M4K, 5K, 5Kc, 5Kf, 20Kc, 24K, 24Kf, 24Kc, 25Kf, ASMACRO, ATLAS, At the Core of the User Experience., BusBridge, CorExtend, CoreFPGA, CoreLV, EC, FastMIPS, JALGO, MALTA, MDMX, MGB, PDtrace, The Pipeline, Pro Series, SEAD, SEAD-2, SmartMIPS, SOC-it and YAMON are among the trademarks of MIPS Technologies, Inc.

All other trademarks referred to herein are the property of their respective owners.

Template: B1.10, Built with tags: 2B MIPS32 PROC

### Table of Contents

| Chapter 1 Introduction to the MIPS32 <sup>TM</sup> M4K <sup>TM</sup> Processor Core |    |

|-------------------------------------------------------------------------------------|----|

| 1.1 Features                                                                        |    |

| 1.2 M4K <sup>™</sup> Core Block Diagram                                             |    |

| 1.2.1 Required Logic Blocks                                                         | 5  |

| 1.2.2 Optional Logic Blocks                                                         | 9  |

| Chapter 2 Pipeline of the M4K <sup>TM</sup> Core                                    | 13 |

| 2.1 Pipeline Stages                                                                 |    |

| 2.1.1 I Stage: Instruction Fetch                                                    |    |

| 2.1.2 E Stage: Execution                                                            |    |

| 2.1.3 M Stage: Memory Fetch                                                         |    |

| 2.1.4 A Stage: Align                                                                |    |

| 2.1.5 W Stage: Writeback                                                            |    |

| 2.2 Multiply/Divide Operations                                                      |    |

| 2.3 MDU Pipeline (High-Performance MDU)                                             |    |

| 2.3.1 32x16 Multiply (High-Performance MDU)                                         |    |

| 2.3.2 32x32 Multiply (High-Performance MDU)                                         |    |

| 2.3.3 Divide (High-Performance MDU)                                                 |    |

| 2.4 MDU Pipeline (Area-Efficient MDU)                                               |    |

| 2.4.1 Multiply (Area-Efficient MDU)                                                 |    |

| 2.4.2 Multiply (Accumulate (Area-Efficient MDU)                                     |    |

| 2.4.3 Divide (Area-Efficient MDU)                                                   |    |

| 2.4.5 Divide (Area-Efficient WDO)                                                   |    |

| 2.6 Data Bypassing                                                                  |    |

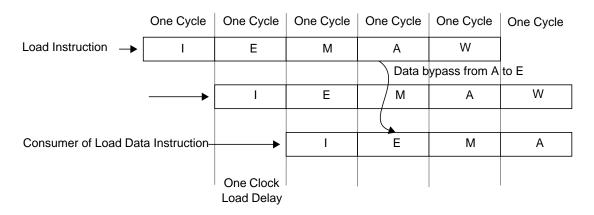

| 2.6.1 Load Delay                                                                    |    |

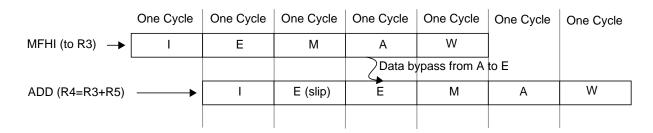

| 2.6.2 Move from HI/LO and CP0 Delay                                                 |    |

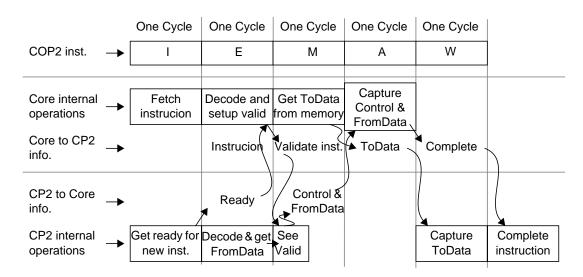

| 2.7 Coprocessor 2 instructions                                                      |    |

| 2.8 Interlock Handling                                                              |    |

| 2.9 Slip Conditions                                                                 |    |

| 2.10 Instruction Interlocks                                                         |    |

| 2.11 Hazards                                                                        |    |

| 2.11.1 Types of Hazards                                                             |    |

| 2.11.1 Types of Hazards 2.11.2 Instruction Listing                                  |    |

| 2.11.2 Histraction Eisting 2.11.3 Eliminating Hazards                               |    |

| 2.11.3 Elithinating Hazards                                                         |    |

| Chapter 3 Memory Management of the M4K <sup>TM</sup> Core                           | 32 |

| 3.1 Introduction                                                                    |    |

| 3.2 Modes of Operation                                                              | 32 |

| 3.2.1 Virtual Memory Segments                                                       |    |

| 3.2.2 User Mode                                                                     | 35 |

| 3.2.3 Kernel Mode                                                                   | 36 |

| 3.2.4 Debug Mode                                                                    | 38 |

| 3.3 Fixed Mapping MMU                                                               | 39 |

| 3.4 System Control Coprocessor                                                      | 42 |

| Chapter 4 Exceptions and Interrupts in the M4K <sup>TM</sup> Core                   | 4  |

| 4.1 Exception Conditions                                                            |    |

| 4.2 Exception Priority                                                              |    |

| 4.3 Interrupts                                                                      |    |

| 4.3.1 Interrupt Modes                                                               |    |

| 4.3.2 Generation of Exception Vector Offsets for Vectored Interrupts                |    |

| 4.4 GPR Shadow Registers                                                     | 54  |

|------------------------------------------------------------------------------|-----|

| 4.5 Exception Vector Locations                                               |     |

| 4.6 General Exception Processing                                             |     |

| 4.7 Debug Exception Processing                                               | 59  |

| 4.8 Exceptions                                                               |     |

| 4.8.1 Reset Exception                                                        | 60  |

| 4.8.2 Soft Reset Exception                                                   | 61  |

| 4.8.3 Debug Single Step Exception                                            |     |

| 4.8.4 Debug Interrupt Exception                                              |     |

| 4.8.5 Non-Maskable Interrupt (NMI) Exception                                 |     |

| 4.8.6 Interrupt Exception                                                    |     |

| 4.8.7 Debug Instruction Break Exception                                      | 63  |

| 4.8.8 Address Error Exception — Instruction Fetch/Data Access                | 64  |

| 4.8.9 Bus Error Exception — Instruction Fetch or Data Access                 |     |

| 4.8.10 Debug Software Breakpoint Exception                                   |     |

| 4.8.11 Execution Exception — System Call                                     | 65  |

| 4.8.12 Execution Exception — Breakpoint                                      |     |

| 4.8.13 Execution Exception — Reserved Instruction                            |     |

| 4.8.14 Execution Exception — Coprocessor Unusable                            |     |

| 4.8.15 Execution Exception — Coprocessor 2 Exception                         |     |

| 4.8.16 Execution Exception — Implementation-Specific 1 exception             |     |

| 4.8.17 Execution Exception — Implementation Specific 2 exception             |     |

| 4.8.18 Execution Exception — Integer Overflow                                |     |

| 4.8.19 Execution Exception — Trap                                            |     |

| 4.8.20 Debug Data Break Exception                                            |     |

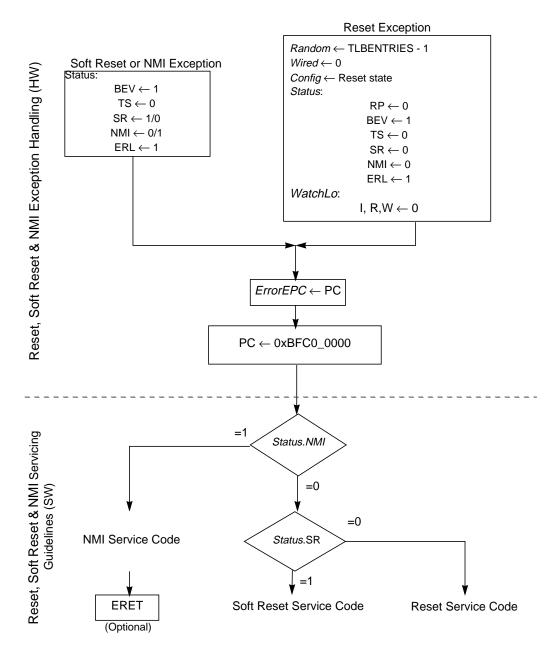

| 4.9 Exception Handling and Servicing Flowcharts                              |     |

|                                                                              |     |

| Chapter 5 CP0 Registers of the M4K <sup>TM</sup> Core                        |     |

| 5.1 CP0 Register Summary                                                     |     |

| 5.2 CP0 Register Descriptions                                                |     |

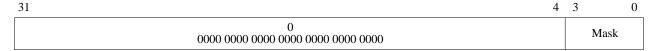

| 5.2.1 HWREna Register (CP0 Register 7, Select 0)                             |     |

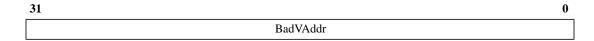

| 5.2.2 BadVAddr Register (CP0 Register 8, Select 0)                           |     |

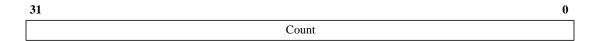

| 5.2.3 Count Register (CP0 Register 9, Select 0)                              |     |

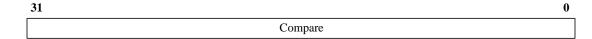

| 5.2.4 Compare Register (CP0 Register 11, Select 0)                           |     |

| 5.2.5 Status Register (CP0 Register 12, Select 0)                            |     |

| 5.2.6 IntCtl Register (CP0 Register 12, Select 1)                            |     |

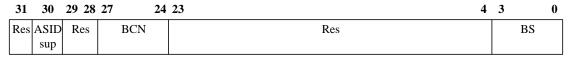

| 5.2.7 SRSCtl Register (CP0 Register 12, Select 2)                            |     |

|                                                                              | 91  |

| 5.2.9 Cause Register (CP0 Register 13, Select 0)                             |     |

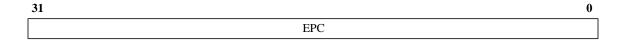

| 5.2.10 Exception Program Counter (CP0 Register 14, Select 0)                 |     |

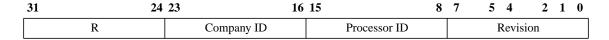

| 5.2.11 Processor Identification (CP0 Register 15, Select 0)                  |     |

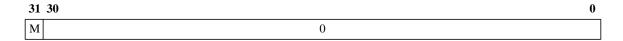

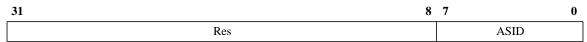

| 5.2.12 EBase Register (CP0 Register 15, Select 1)                            |     |

| 5.2.13 Config Register (CP0 Register 16, Select 0)                           |     |

| 5.2.14 Config1 Register (CP0 Register 16, Select 1)                          |     |

| 5.2.15 Config2 Register (CP0 Register 16, Select 2)                          |     |

| 5.2.16 Config3 Register (CP0 Register 16, Select 3)                          |     |

| 5.2.17 Debug Register (CP0 Register 23, Select 0)                            |     |

| 5.2.18 Trace Control Register (CP0 Register 23, Select 1)                    |     |

| 5.2.19 Trace Control2 Register (CP0 Register 23, Select 2)                   |     |

| 5.2.20 User Trace Data Register (CP0 Register 23, Select 3)                  |     |

| 5.2.21 TraceBPC Register (CP0 Register 23, Select 4)                         |     |

| 5.2.22 Debug Exception Program Counter Register (CP0 Register 24, Select 0)  |     |

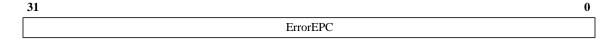

| 5.2.23 ErrorEPC (CP0 Register 30, Select 0)                                  |     |

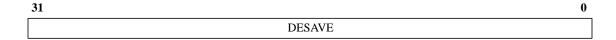

| 5.2.24 DeSave Register (CP0 Register 31, Select 0)                           | 118 |

| Chapter 6 Hardware and Software Initialization of the M4K <sup>TM</sup> Core | 121 |

| Chapter o traituware and Software initialization of the M4x Cole             | 121 |

| 6.1 Hardware-Initialized Processor State                                       | 121 |

|--------------------------------------------------------------------------------|-----|

| 6.1.1 Coprocessor 0 State                                                      | 121 |

| 6.1.2 Bus State Machines                                                       |     |

| 6.1.3 Static Configuration Inputs                                              | 122 |

| 6.1.4 Fetch Address                                                            |     |

| 6.2 Software Initialized Processor State                                       |     |

| 6.2.1 Register File                                                            |     |

| 6.2.2 Coprocessor 0 State                                                      |     |

| •                                                                              |     |

| Chapter 7 Power Management of the M4K <sup>TM</sup> Core                       |     |

| 7.1 Register-Controlled Power Management                                       | 124 |

| 7.2 Instruction-Controlled Power Management                                    | 125 |

| Chapter 8 EJTAG Debug Support in the M4K <sup>TM</sup> Core                    | 129 |

| 8.1 Debug Control Register                                                     |     |

| 8.2 Hardware Breakpoints                                                       |     |

| 8.2.1 Features of Instruction Breakpoint                                       |     |

| 8.2.2 Features of Data Breakpoint                                              |     |

| 8.2.3 Instruction Breakpoint Registers Overview                                |     |

| 8.2.4 Data Breakpoint Registers Overview                                       |     |

| 8.2.5 Conditions for Matching Breakpoints                                      |     |

| 8.2.6 Debug Exceptions from Breakpoints                                        |     |

| 8.2.7 Breakpoint used as TriggerPoint                                          |     |

| 8.2.8 Instruction Breakpoint Registers                                         |     |

| 8.2.9 Data Breakpoint Registers                                                |     |

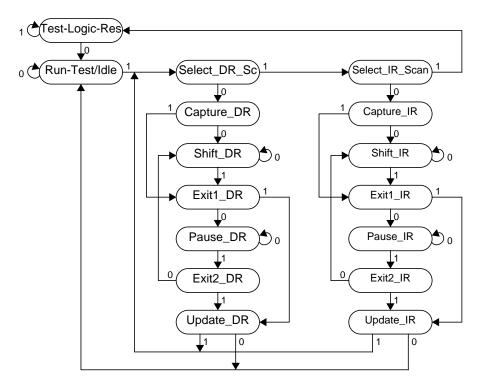

| 8.3 Test Access Port (TAP)                                                     |     |

| 8.3.1 EJTAG Internal and External Interfaces                                   |     |

| 8.3.2 Test Access Port Operation                                               |     |

| 8.3.3 Test Access Port (TAP) Instructions                                      |     |

| 8.4 EJTAG TAP Registers                                                        |     |

| 8.4.1 Instruction Register                                                     |     |

| · · · · · · · · · · · · · · · · · · ·                                          |     |

| 8.4.2 Data Registers Overview                                                  |     |

| 8.4.3 Processor Access Address Register                                        |     |

| 8.4.4 Fastdata Register (TAP Instruction FASTDATA)  8.5 TAP Processor Accesses |     |

|                                                                                |     |

| 8.6 Fetch/Load and Store from/to the EJTAG Probe through dmseg                 |     |

| 8.7 EJTAG Trace                                                                |     |

| 8.7.1 Processor Modes                                                          |     |

| 8.7.2 Software versus Hardware control                                         |     |

| 8.7.3 Trace information                                                        |     |

| 8.7.4 Load/Store address and data trace information                            |     |

| 8.7.5 Programmable processor trace mode options                                |     |

| 8.7.6 Programmable trace information options                                   |     |

| 8.7.7 Enable trace to probe/on-chip memory                                     |     |

| 8.7.8 TCB Trigger                                                              |     |

| 8.7.9 Cycle by cycle information                                               |     |

| 8.7.10 Trace Message Format                                                    |     |

| 8.7.11 Trace Word Format                                                       |     |

| 8.8 PDtrace <sup>TM</sup> Registers (software control)                         |     |

| 8.9 Trace Control Block (TCB) Registers (hardware control)                     |     |

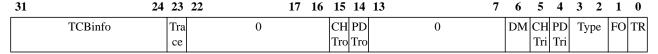

| 8.9.1 TCBCONTROLA Register                                                     |     |

| 8.9.2 TCBCONTROLB Register                                                     |     |

| 8.9.3 TCBDATA Register                                                         |     |

| 8.9.4 TCBCONFIG Register (Reg 0)                                               |     |

| 8.9.5 TCBTW Register (Reg 4)                                                   |     |

| 8.9.6 TCBRDP Register (Reg 5)                                                  | 183 |

| 8.9.7 TCBWRP Register (Reg 6)                                                  | 183 |

|--------------------------------------------------------------------------------|-----|

| 8.9.8 TCBSTP Register (Reg 7)                                                  |     |

| 8.9.9 <i>TCBTRIGx</i> Register (Reg 16-23)                                     | 184 |

| 8.9.10 Register Reset State                                                    | 186 |

| 8.10 EJTAG Trace Enabling                                                      | 187 |

| 8.10.1 Trace Trigger from EJTAG Hardware Instruction/Data Breakpoints          | 187 |

| 8.10.2 Turning On PDtrace™ Trace                                               | 187 |

| 8.10.3 Turning Off PDtrace™ Trace                                              | 188 |

| 8.10.4 TCB Trace Enabling                                                      | 189 |

| 8.10.5 Tracing a reset exception                                               |     |

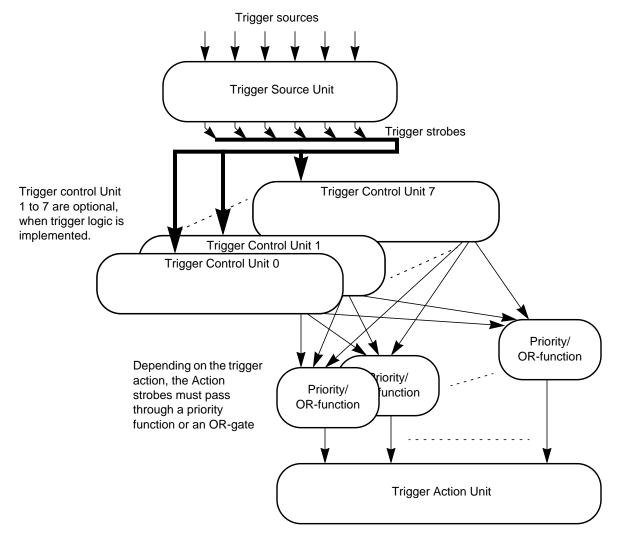

| 8.11 TCB Trigger logic                                                         |     |

| 8.11.1 Trigger units overview                                                  |     |

| 8.11.2 Trigger Source Unit                                                     |     |

| 8.11.3 Trigger Control Units                                                   |     |

| 8.11.4 Trigger Action Unit                                                     |     |

| 8.11.5 Simultaneous triggers                                                   |     |

| 8.12 EJTAG Trace cycle-by-cycle behavior                                       |     |

| 8.12.1 Fifo logic in PDtrace and TCB modules                                   |     |

| 8.12.2 Handling of Fifo overflow in the PDtrace module                         |     |

| 8.12.3 Handling of Fifo overflow in the TCB                                    |     |

| 8.12.4 Adding cycle accurate information to the trace                          |     |

| 8.13 TCB On-Chip Trace Memory                                                  |     |

| 8.13.1 On-Chip Trace Memory size                                               |     |

| 8.13.2 Trace-From Mode                                                         |     |

| 8.13.3 Trace-To Mode                                                           | 194 |

| Chapter 9 Instruction Set Overview                                             | 196 |

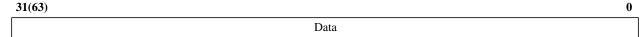

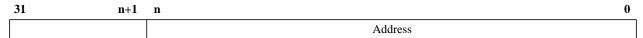

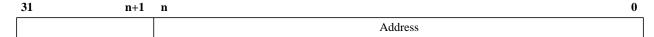

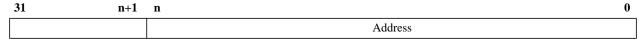

| 9.1 CPU Instruction Formats                                                    | 196 |

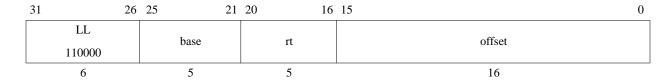

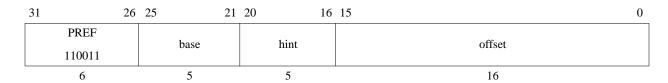

| 9.2 Load and Store Instructions                                                | 197 |

| 9.2.1 Scheduling a Load Delay Slot                                             | 197 |

| 9.2.2 Defining Access Types                                                    |     |

| 9.3 Computational Instructions                                                 | 198 |

| 9.3.1 Cycle Timing for Multiply and Divide Instructions                        |     |

| 9.4 Jump and Branch Instructions                                               |     |

| 9.4.1 Overview of Jump Instructions                                            |     |

| 9.4.2 Overview of Branch Instructions                                          |     |

| 9.5 Control Instructions                                                       |     |

| 9.6 Coprocessor Instructions                                                   | 199 |

| Chapter 10 M4K <sup>TM</sup> Processor Core Instructions                       | 202 |

| 10.1 Understanding the Instruction Descriptions                                | 202 |

| 10.2 M4K <sup>TM</sup> Opcode Map                                              |     |

| 10.3 MIPS32 <sup>TM</sup> Instruction Set for the M4K <sup>TM</sup> core       | 205 |

| Chapter 11 MIPS16 Application-Specific Extension to the MIPS32 Instruction Set | 228 |

| 11.1 Instruction Bit Encoding                                                  |     |

| 11.2 Instruction Listing                                                       |     |

| Appendix A Revision History                                                    | 234 |

|                                                                                |     |

## List of Figures

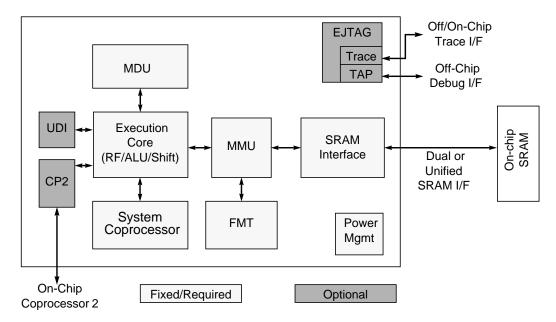

| Figure 1-1: M4K <sup>TM</sup> Processor Core Block Diagram                                      | 5   |

|-------------------------------------------------------------------------------------------------|-----|

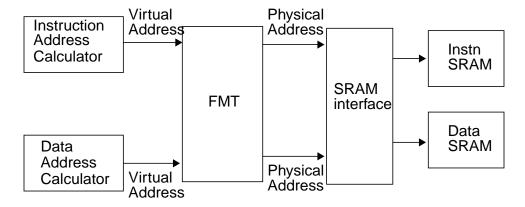

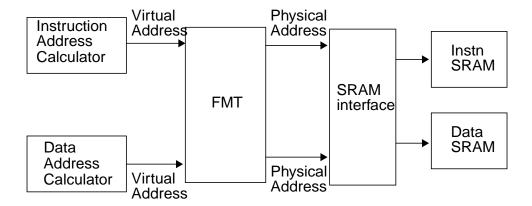

| Figure 1-2: Address Translation During a SRAM Access                                            |     |

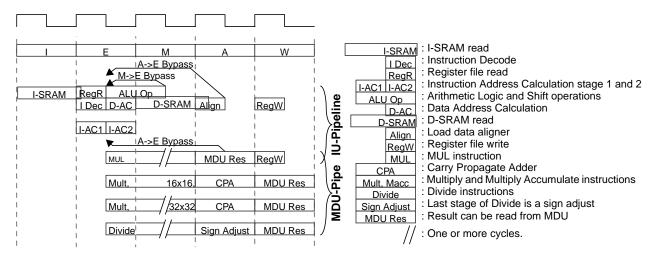

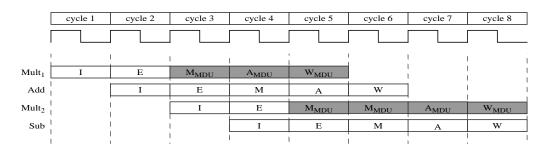

| Figure 2-1: M4K <sup>TM</sup> Core Pipeline Stages (with high-performance MDU)                  |     |

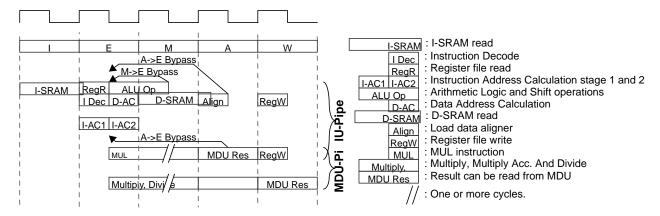

| Figure 2-2: M4K <sup>TM</sup> Core Pipeline Stages (with area-efficient MDU)                    |     |

| Figure 2-3: MDU Pipeline Behavior During Multiply Operations                                    |     |

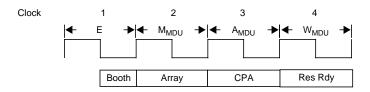

| Figure 2-4: MDU Pipeline Flow During a 32x16 Multiply Operation                                 |     |

| Figure 2-5: MDU Pipeline Flow During a 32x32 Multiply Operation                                 |     |

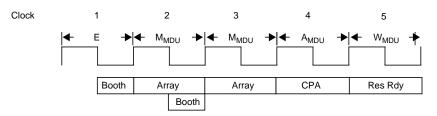

| Figure 2-6: High-Performance MDU Pipeline Flow During a 8-bit Divide (DIV) Operation            |     |

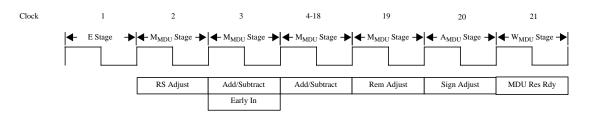

| Figure 2-7: High-Performance MDU Pipeline Flow During a 16-bit Divide (DIV) Operation           |     |

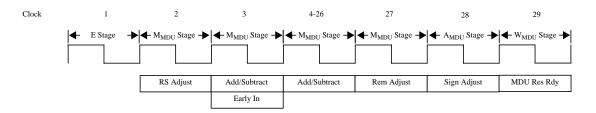

| Figure 2-8: High-Performance MDU Pipeline Flow During a 24-bit Divide (DIV) Operation           |     |

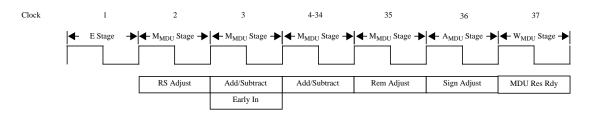

| Figure 2-9: High-Performance MDU Pipeline Flow During a 32-bit Divide (DIV) Operation           |     |

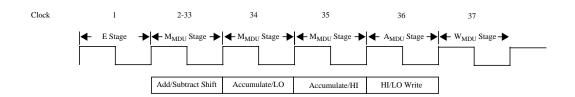

| Figure 2-10: M4K <sup>TM</sup> Area-Efficient MDU Pipeline Flow During a Multiply Operation     |     |

| Figure 2-11: M4KC Area-Efficient MDU Pipeline Flow During a Multiply Accumulate Operation       |     |

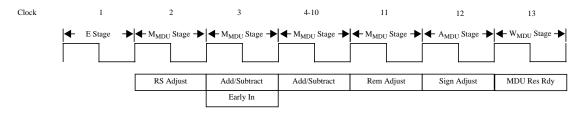

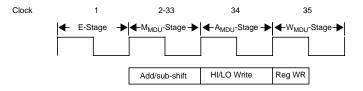

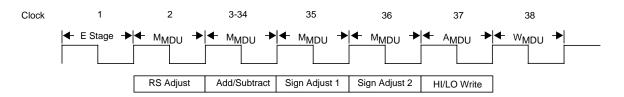

| Figure 2-12: M4K <sup>TM</sup> Area-Efficient MDU Pipeline Flow During a Divide (DIV) Operation |     |

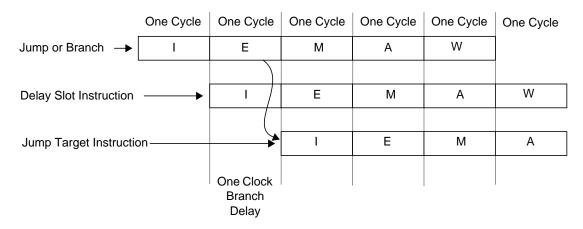

| Figure 2-13: IU Pipeline Branch Delay                                                           |     |

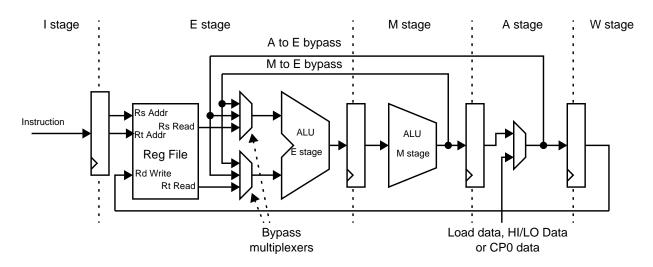

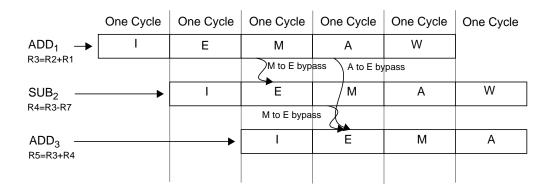

| Figure 2-14: IU Pipeline Data bypass                                                            |     |

| Figure 2-15: IU Pipeline M to E bypass                                                          |     |

| Figure 2-16: IU Pipeline A to E Data bypass                                                     |     |

| Figure 2-17: IU Pipeline Slip after a MFHI                                                      |     |

| Figure 2-18: Coprocessor 2 Interface Transactions                                               |     |

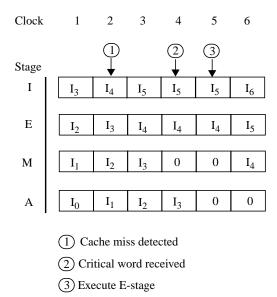

| Figure 2-18: Coprocessor 2 Interface Transactions.  Figure 2-19: Instruction Cache Miss Slip    |     |

|                                                                                                 |     |

| Figure 3-1: Address Translation During SRAM Access                                              |     |

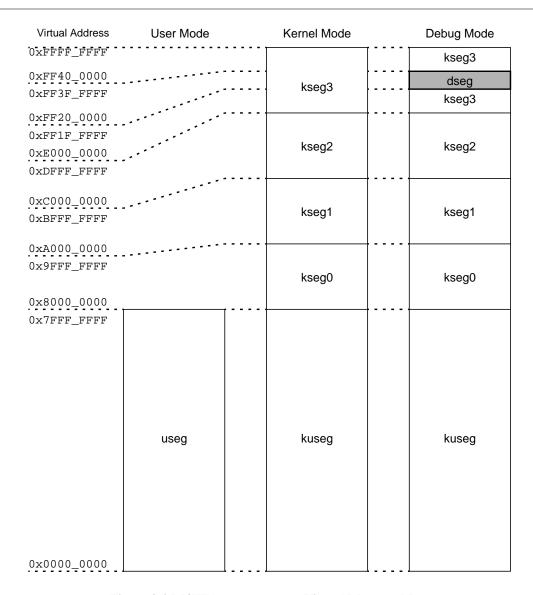

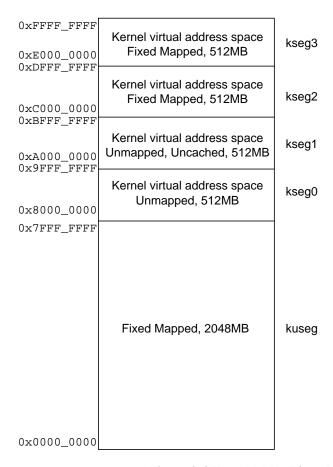

| Figure 3-2: M4K <sup>TM</sup> processor core Virtual Memory Map.                                |     |

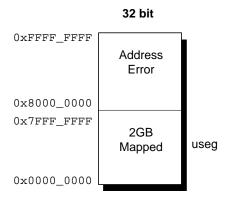

| Figure 3-3: User Mode Virtual Address Space                                                     |     |

| Figure 3-4: Kernel Mode Virtual Address Space                                                   |     |

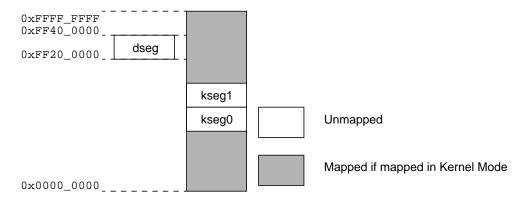

| Figure 3-5: Debug Mode Virtual Address Space                                                    |     |

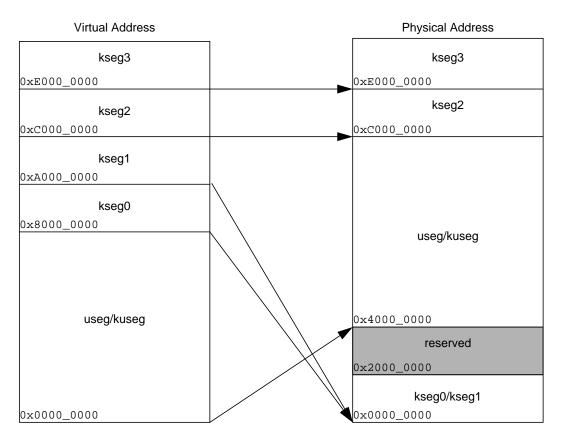

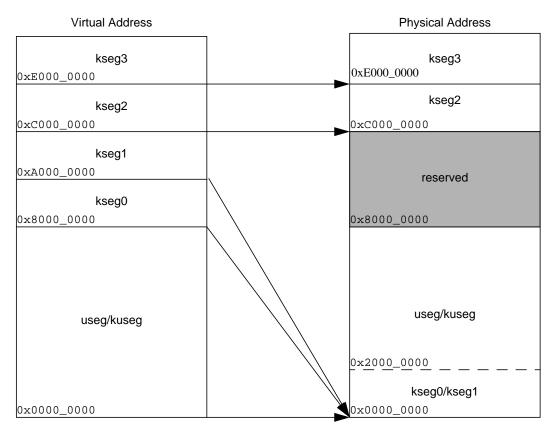

| Figure 3-6: FM Memory Map (ERL=0) in the M4K <sup>TM</sup> Processor Core                       |     |

| Figure 3-7: FM Memory Map (ERL=1) in the M4K <sup>TM</sup> Processor Core                       |     |

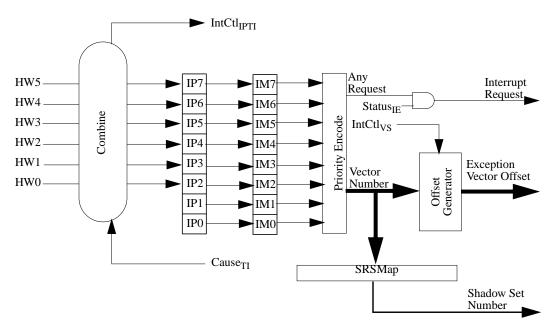

| Figure 4-1: Interrupt Generation for Vectored Interrupt Mode                                    |     |

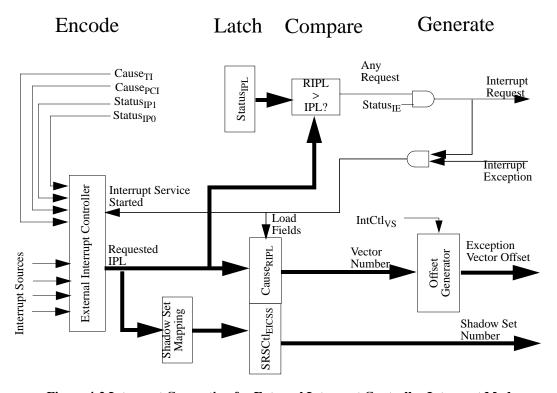

| Figure 4-2: Interrupt Generation for External Interrupt Controller Interrupt Mode               |     |

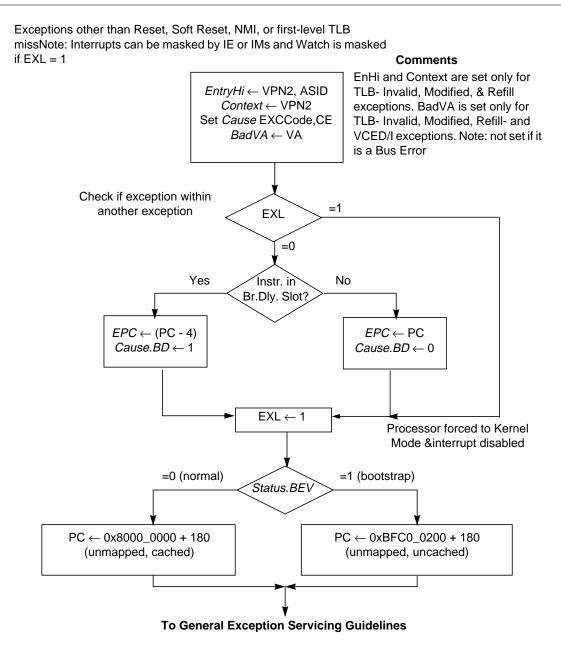

| Figure 4-3: General Exception Handler (HW)                                                      |     |

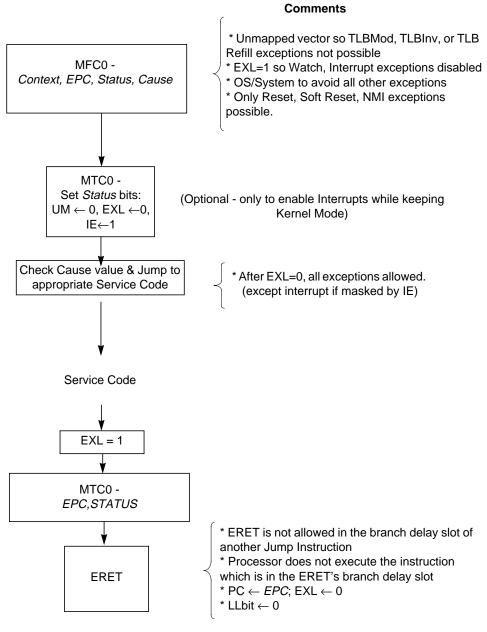

| Figure 4-4: General Exception Servicing Guidelines (SW)                                         |     |

| Figure 4-5: Reset, Soft Reset and NMI Exception Handling and Servicing Guidelines               |     |

| Figure 5-1: HWREna Register Format                                                              |     |

| Figure 5-2: BadVAddr Register Format                                                            |     |

| Figure 5-3: Count Register Format                                                               |     |

| Figure 5-4: Compare Register Format                                                             |     |

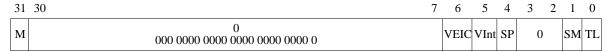

| Figure 5-5: Status Register Format                                                              |     |

| Figure 5-6: IntCtl Register Format                                                              |     |

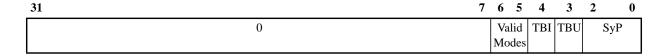

| Figure 5-7: SRSCtl Register Format                                                              |     |

| Figure 5-8: SRSMap Register Format                                                              |     |

| Figure 5-9: Cause Register Format.                                                              |     |

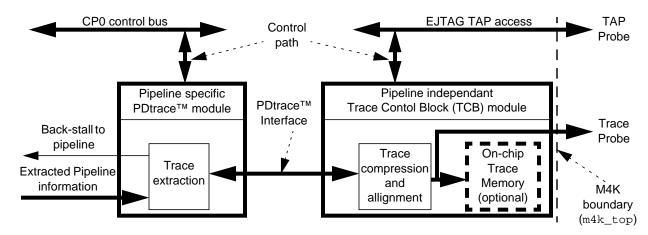

| Figure 5-10: EPC Register Format                                                                |     |

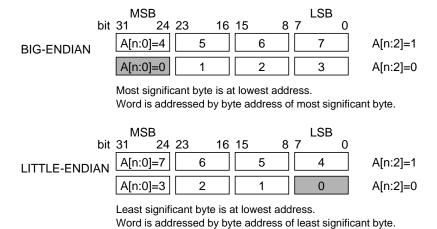

| Figure 5-11: PRId Register Format                                                               |     |

| Figure 5-12: EBase Register Format                                                              |     |

| Figure 5-13: Config Register Format — Select 0                                                  |     |

| Figure 5-14: Config Register Field Descriptions                                                 |     |

| Figure 5-15: Config1 Register Format — Select 1                                                 |     |

| Figure 5-16: Config2 Register Format — Select 2                                                 | 103 |

| Figure 5-17: Config3 Register Format                                                            | 104 |

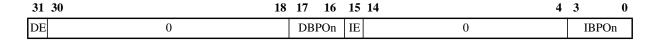

| Figure 5-18: <i>Debug</i> Register Format                                               | 106 |

|-----------------------------------------------------------------------------------------|-----|

| Figure 5-19: Trace Control Register Format                                              | 109 |

| Figure 5-20: Trace Control2 Register Format.                                            | 112 |

| Figure 5-21: User Trace Data Register Format                                            |     |

| Figure 5-22: Trace BPC Register Format                                                  |     |

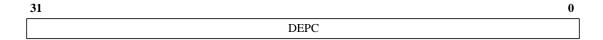

| Figure 5-23: DEPC Register Format                                                       |     |

| Figure 5-24: ErrorEPC Register Format.                                                  |     |

| Figure 5-25: DeSave Register Format                                                     | 118 |

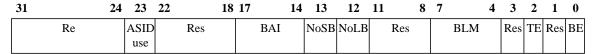

| Figure 8-1: TAP Controller State Diagram                                                |     |

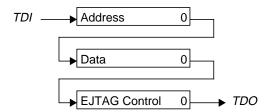

| Figure 8-2: Concatenation of the EJTAG Address, Data and Control Registers              | 157 |

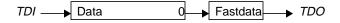

| Figure 8-3: TDI to TDO Path when in Shift-DR State and FASTDATA Instruction is Selected | 157 |

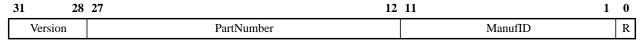

| Figure 8-4: Endian Formats for the <i>PAD</i> Register                                  | 165 |

| Figure 8-5: EJTAG Trace modules in the M4K <sup>TM</sup> core                           | 169 |

| Figure 8-6: TCB Trigger processing overview                                             | 190 |

| Figure 9-1: Instruction Formats                                                         |     |

### List of Tables

| Table 2-1: MDU Instruction Latencies (High-Performance MDU)                                |     |

|--------------------------------------------------------------------------------------------|-----|

| Table 2-2: MDU Instruction Repeat Rates (High-Performance MDU)                             |     |

| Table 2-3: M4K <sup>TM</sup> Core Instruction Latencies (Area-Efficient MDU)               |     |

| Table 2-4: Pipeline Interlocks                                                             |     |

| Table 2-5: Instruction Interlocks                                                          |     |

| Table 2-6: Execution Hazards                                                               |     |

| Table 2-7: Instruction Hazards                                                             |     |

| Table 2-8: Hazard Instruction Listing                                                      |     |

| Table 3-1: User Mode Segments                                                              |     |

| Table 3-2: Kernel Mode Segments                                                            |     |

| Table 3-3: Physical Address and Cache Attributes for dseg, dmseg, and drseg Address Spaces |     |

| Table 3-4: CPU Access to drseg Address Range                                               |     |

| Table 3-5: CPU Access to dmseg Address Range                                               |     |

| Table 3-6: Cache Coherency Attributes                                                      | 40  |

| Table 4-1: Priority of Exceptions                                                          |     |

| Table 4-1: Priority of Exceptions  Table 4-2: Interrupt Modes                              |     |

| Table 4-3: Relative Interrupt Priority for Vectored Interrupt Mode                         |     |

| Table 4-4: Exception Vector Offsets for Vectored Interrupts                                |     |

| Table 4-5: Exception Vector Base Addresses                                                 |     |

| Table 4-6: Exception Vector Offsets                                                        |     |

| Table 4-7: Exception Vector Offsets                                                        |     |

| Table 4-8: Value Stored in EPC, ErrorEPC, or DEPC on an Exception                          |     |

| Table 4-9: Debug Exception Vector Addresses                                                |     |

| Table 4-10: Register States an Interrupt Exception                                         |     |

| Table 4-11: CP0 Register States on an Address Exception Error                              |     |

| Table 4-12: Register States on a Coprocessor Unusable Exception                            |     |

| Table 5-1: CP0 Registers                                                                   |     |

| Table 5-2: CP0 Register Field Types                                                        |     |

| Table 5-4: HWREna Register Field Descriptions                                              |     |

| Table 5-5: BadVAddr Register Field Description                                             |     |

| Table 5-6: Count Register Field Description                                                |     |

| Table 5-7: Compare Register Field Description                                              |     |

| Table 5-8: Status Register Field Descriptions                                              |     |

| Table 5-9: IntCtl Register Field Descriptions                                              |     |

| Table 5-10: SRSCtl Register Field Descriptions                                             |     |

| Table 5-11: Sources for new SRSCtl <sub>CSS</sub> on an Exception or Interrupt             | 89  |

| Table 5-12: SRSMap Register Field Descriptions                                             | 91  |

| Table 5-13: Cause Register Field Descriptions                                              | 92  |

| Table 5-14: Cause Register ExcCode Field                                                   | 95  |

| Table 5-15: EPC Register Field Description                                                 | 96  |

| Table 5-16: PRId Register Field Descriptions                                               |     |

| Table 5-17: EBase Register Field Descriptions                                              |     |

| Table 5-18: Cache Coherency Attributes                                                     |     |

| Table 5-19: Config1 Register Field Descriptions — Select 1                                 |     |

| Table 5-20: Config1 Register Field Descriptions — Select 1                                 |     |

| Table 5-21: Config3 Register Field Descriptions                                            |     |

| Table 5-22: Debug Register Field Descriptions                                              |     |

| Table 5-23: TraceControl Register Field Descriptions                                       |     |

| Table 5-24: TraceControl2 Register Field Descriptions                                      | 112 |

| Table 5-25: UserTraceData Register Field Descriptions                     | 114 |

|---------------------------------------------------------------------------|-----|

| Table 5-26: TraceBPC Register Field Descriptions                          |     |

| Table 5-27: DEPC Register Formats                                         |     |

| Table 5-28: ErrorEPC Register Field Description                           |     |

| Table 5-29: DeSave Register Field Description                             |     |

| Table 8-1: Debug Control Register Field Descriptions                      |     |

| Table 8-2: Overview of Status Register for Instruction Breakpoints        |     |

| Table 8-3: Overview of Registers for Each Instruction Breakpoint          |     |

| Table 8-4: Overview of Status Register for Data Breakpoints               |     |

| Table 8-5: Overview of Registers for each Data Breakpoint                 |     |

| Table 8-6: Addresses for Instruction Breakpoint Registers                 |     |

| Table 8-7: IBS Register Field Descriptions                                |     |

| Table 8-8: <i>IBAn</i> Register Field Descriptions                        |     |

| Table 8-9: <i>IBMn</i> Register Field Descriptions                        |     |

| Table 8-10: <i>IBASIDn</i> Register Field Descriptions                    |     |

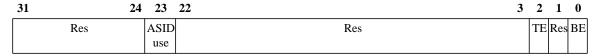

| Table 8-11: <i>IBCn</i> Register Field Descriptions                       |     |

| Table 8-12: Addresses for Data Breakpoint Registers                       |     |

| Table 8-13: DBS Register Field Descriptions                               |     |

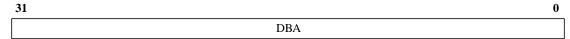

| Table 8-14: <i>DBAn</i> Register Field Descriptions                       |     |

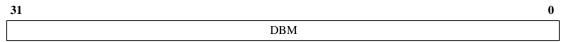

| Table 8-15: <i>DBMn</i> Register Field Descriptions                       |     |

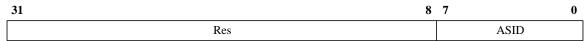

| Table 8-16: <i>DBASIDn</i> Register Field Descriptions                    |     |

| Table 8-17: <i>DBCn</i> Register Field Descriptions                       |     |

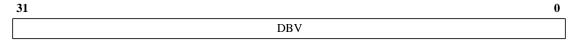

| Table 8-18: <i>DBVn</i> Register Field Descriptions                       |     |

| Table 8-19: EJTAG Interface Pins                                          |     |

| Table 8-20: Implemented EJTAG Instructions                                |     |

| Table 8-21: Device Identification Register                                |     |

| Table 8-22: Implementation Register Descriptions                          |     |

| Table 8-23: EJTAG Control Register Descriptions                           |     |

|                                                                           |     |

| Table 8-24: Fastdata Register Field Description                           |     |

| Table 8-25: Operation of the FASTDATA access                              |     |

| Table 8-26: A List of Coprocessor 0 Trace Registers                       |     |

| Table 8-27: TCB EJTAG registers                                           |     |

| Table 8-28: Registers selected by TCBCONTROLA Registers Field Proprietors |     |

| Table 8-29: TCBCONTROLA Register Field Descriptions                       |     |

| Table 8-30: TCBCONTROLB Register Field Descriptions                       |     |

| Table 8-31: Clock Ratio encoding of the CR field                          |     |

| Table 8-32: TCBOANIC Parists Field Descriptions                           |     |

| Table 8-33: TCBCONFIG Register Field Descriptions                         |     |

| Table 8-34: TCBTW Register Field Descriptions                             |     |

| Table 8-35: TCBRDP Register Field Descriptions                            |     |

| Table 8-36: TCBWRP Register Field Descriptions                            |     |

| Table 8-37: TCBSTP Register Field Descriptions                            |     |

| Table 8-38: TCBTRIGx Register Field Descriptions                          |     |

| Table 9-1: Byte Access Within a Word                                      |     |

| Table 10-1: Encoding of the <i>Opcode</i> Field                           |     |

| Table 10-2: Special Opcode encoding of Function Field                     |     |

| Table 10-3: Special2 Opcode Encoding of Function Field                    |     |

| Table 10-4: Special3 Opcode Encoding of Function Field                    |     |

| Table 10-5: RegImm Encoding of rt Field                                   |     |

| Table 10-6: COP2 Encoding of rs Field                                     |     |

| Table 10-7: COP2 Encoding of rt Field When rs=BC2                         |     |

| Table 10-8: COP0 Encoding of rs Field                                     |     |

| Table 10-9: COPO Encoding of Function Field When rs=CO                    |     |

| Table 10-10: Instruction Set                                              |     |

| Table 10-11: Values of the <i>hint</i> Field for the PREF Instruction     | 216 |

| Table 11-2: MIPS16 Encoding of the Opcode Field       229         Table 11-3: MIPS16 JAL(X) Encoding of the x Field       229         Table 11-4: MIPS16 SHIFT Encoding of the f Field       229         Table 11-5: MIPS16 RRI-A Encoding of the f Field       229         Table 11-6: MIPS16 I8 Encoding of the funct Field       229         Table 11-7: MIPS16 RRR Encoding of the Field       230         Table 11-8: MIPS16 RR Encoding of the Funct Field       230         Table 11-9: MIPS16 I8 Encoding of the s Field when funct=SVRS       230         Table 11-10: MIPS16 RR Encoding of the ry Field when funct=J(AL)R(C)       230         Table 11-11: MIPS16 RR Encoding of the ry Field when funct=CNVT       230         Table 11-12: MIPS16 Load and Store Instructions       231         Table 11-13: MIPS16 Save and Restore Instructions       231         Table 11-15: MIPS16 ALU Immediate Instructions       231         Table 11-15: MIPS16 Apichametic Two or Three Operand Register Instructions       231         Table 11-16: MIPS16 Special Instructions       232         Table 11-17: MIPS16 Multiply and Divide Instructions       232         Table 11-18: MIPS16 Shift Instructions       233         Table 11-19: MIPS16 Shift Instructions       233         Table 11-19: MIPS16 Shift Instructions       233         Table A-1: Revision History <t< th=""><th>Table 11-1: Symbols Used in the Instruction Encoding Tables</th><th>228</th></t<> | Table 11-1: Symbols Used in the Instruction Encoding Tables               | 228 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----|

| Table 11-3: MIPS16 JAL(X) Encoding of the x Field229Table 11-4: MIPS16 SHIFT Encoding of the f Field229Table 11-5: MIPS16 RRI-A Encoding of the f Field229Table 11-6: MIPS16 I8 Encoding of the funct Field229Table 11-7: MIPS16 RRR Encoding of the Field230Table 11-8: MIPS16 I8 Encoding of the Funct Field230Table 11-9: MIPS16 I8 Encoding of the s Field when funct=SVRS230Table 11-10: MIPS16 RR Encoding of the ry Field when funct=J(AL)R(C)230Table 11-11: MIPS16 RR Encoding of the ry Field when funct=CNVT230Table 11-12: MIPS16 Load and Store Instructions230Table 11-13: MIPS16 Save and Restore Instructions231Table 11-14: MIPS16 ALU Immediate Instructions231Table 11-15: MIPS16 Arithmetic Two or Three Operand Register Instructions231Table 11-16: MIPS16 Special Instructions232Table 11-17: MIPS16 Multiply and Divide Instructions232Table 11-18: MIPS16 Jump and Branch Instructions232                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                           |     |

| Table 11-4: MIPS16 SHIFT Encoding of the f Field229Table 11-5: MIPS16 RRI-A Encoding of the f Field229Table 11-6: MIPS16 I8 Encoding of the funct Field229Table 11-7: MIPS16 RRR Encoding of the Field230Table 11-8: MIPS16 I8 Encoding of the Funct Field230Table 11-9: MIPS16 I8 Encoding of the s Field when funct=SVRS230Table 11-10: MIPS16 RR Encoding of the ry Field when funct=J(AL)R(C)230Table 11-11: MIPS16 RR Encoding of the ry Field when funct=CNVT230Table 11-12: MIPS16 Load and Store Instructions230Table 11-13: MIPS16 Save and Restore Instructions231Table 11-14: MIPS16 ALU Immediate Instructions231Table 11-15: MIPS16 Arithmetic Two or Three Operand Register Instructions231Table 11-16: MIPS16 Special Instructions231Table 11-17: MIPS16 Multiply and Divide Instructions232Table 11-18: MIPS16 Jump and Branch Instructions232                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                           |     |

| Table 11-5: MIPS16 RRI-A Encoding of the f Field229Table 11-6: MIPS16 I8 Encoding of the funct Field230Table 11-7: MIPS16 RRR Encoding of the Field230Table 11-8: MIPS16 RR Encoding of the Funct Field230Table 11-9: MIPS16 I8 Encoding of the s Field when funct=SVRS230Table 11-10: MIPS16 RR Encoding of the ry Field when funct=J(AL)R(C)230Table 11-11: MIPS16 RR Encoding of the ry Field when funct=CNVT230Table 11-12: MIPS16 Load and Store Instructions230Table 11-13: MIPS16 Save and Restore Instructions231Table 11-14: MIPS16 ALU Immediate Instructions231Table 11-15: MIPS16 Arithmetic Two or Three Operand Register Instructions231Table 11-16: MIPS16 Special Instructions232Table 11-17: MIPS16 Multiply and Divide Instructions232Table 11-18: MIPS16 Jump and Branch Instructions232                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                           |     |

| Table 11-6: MIPS16 I8 Encoding of the funct Field229Table 11-7: MIPS16 RRR Encoding of the f Field230Table 11-8: MIPS16 RR Encoding of the Funct Field230Table 11-9: MIPS16 I8 Encoding of the s Field when funct=SVRS230Table 11-10: MIPS16 RR Encoding of the ry Field when funct=J(AL)R(C)230Table 11-11: MIPS16 RR Encoding of the ry Field when funct=CNVT230Table 11-12: MIPS16 Load and Store Instructions230Table 11-13: MIPS16 Save and Restore Instructions231Table 11-14: MIPS16 ALU Immediate Instructions231Table 11-15: MIPS16 Arithmetic Two or Three Operand Register Instructions231Table 11-16: MIPS16 Special Instructions232Table 11-17: MIPS16 Multiply and Divide Instructions232Table 11-18: MIPS16 Jump and Branch Instructions232                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                           |     |

| Table 11-8: MIPS16 RR Encoding of the Funct Field230Table 11-9: MIPS16 I8 Encoding of the s Field when funct=SVRS230Table 11-10: MIPS16 RR Encoding of the ry Field when funct=J(AL)R(C)230Table 11-11: MIPS16 RR Encoding of the ry Field when funct=CNVT230Table 11-12: MIPS16 Load and Store Instructions230Table 11-13: MIPS16 Save and Restore Instructions231Table 11-14: MIPS16 ALU Immediate Instructions231Table 11-15: MIPS16 Arithmetic Two or Three Operand Register Instructions231Table 11-16: MIPS16 Special Instructions232Table 11-17: MIPS16 Multiply and Divide Instructions232Table 11-18: MIPS16 Jump and Branch Instructions232                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           |     |

| Table 11-9: MIPS16 I8 Encoding of the s Field when funct=SVRS230Table 11-10: MIPS16 RR Encoding of the ry Field when funct=J(AL)R(C)230Table 11-11: MIPS16 RR Encoding of the ry Field when funct=CNVT230Table 11-12: MIPS16 Load and Store Instructions230Table 11-13: MIPS16 Save and Restore Instructions231Table 11-14: MIPS16 ALU Immediate Instructions231Table 11-15: MIPS16 Arithmetic Two or Three Operand Register Instructions231Table 11-16: MIPS16 Special Instructions232Table 11-17: MIPS16 Multiply and Divide Instructions232Table 11-18: MIPS16 Jump and Branch Instructions232                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Table 11-7: MIPS16 RRR Encoding of the f Field                            | 230 |

| Table 11-10: MIPS16 RR Encoding of the ry Field when funct=J(AL)R(C)230Table 11-11: MIPS16 RR Encoding of the ry Field when funct=CNVT230Table 11-12: MIPS16 Load and Store Instructions230Table 11-13: MIPS16 Save and Restore Instructions231Table 11-14: MIPS16 ALU Immediate Instructions231Table 11-15: MIPS16 Arithmetic Two or Three Operand Register Instructions231Table 11-16: MIPS16 Special Instructions232Table 11-17: MIPS16 Multiply and Divide Instructions232Table 11-18: MIPS16 Jump and Branch Instructions232                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Table 11-8: MIPS16 RR Encoding of the Funct Field                         | 230 |

| Table 11-11: MIPS16 RR Encoding of the ry Field when funct=CNVT230Table 11-12: MIPS16 Load and Store Instructions230Table 11-13: MIPS16 Save and Restore Instructions231Table 11-14: MIPS16 ALU Immediate Instructions231Table 11-15: MIPS16 Arithmetic Two or Three Operand Register Instructions231Table 11-16: MIPS16 Special Instructions232Table 11-17: MIPS16 Multiply and Divide Instructions232Table 11-18: MIPS16 Jump and Branch Instructions232                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Table 11-9: MIPS16 I8 Encoding of the s Field when funct=SVRS             | 230 |

| Table 11-12: MIPS16 Load and Store Instructions230Table 11-13: MIPS16 Save and Restore Instructions231Table 11-14: MIPS16 ALU Immediate Instructions231Table 11-15: MIPS16 Arithmetic Two or Three Operand Register Instructions231Table 11-16: MIPS16 Special Instructions232Table 11-17: MIPS16 Multiply and Divide Instructions232Table 11-18: MIPS16 Jump and Branch Instructions232                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Table 11-10: MIPS16 RR Encoding of the ry Field when funct=J(AL)R(C)      | 230 |

| Table 11-13: MIPS16 Save and Restore Instructions231Table 11-14: MIPS16 ALU Immediate Instructions231Table 11-15: MIPS16 Arithmetic Two or Three Operand Register Instructions231Table 11-16: MIPS16 Special Instructions232Table 11-17: MIPS16 Multiply and Divide Instructions232Table 11-18: MIPS16 Jump and Branch Instructions232                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Table 11-11: MIPS16 RR Encoding of the ry Field when funct=CNVT           | 230 |

| Table 11-14: MIPS16 ALU Immediate Instructions231Table 11-15: MIPS16 Arithmetic Two or Three Operand Register Instructions231Table 11-16: MIPS16 Special Instructions232Table 11-17: MIPS16 Multiply and Divide Instructions232Table 11-18: MIPS16 Jump and Branch Instructions232                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                           |     |

| Table 11-15: MIPS16 Arithmetic Two or Three Operand Register Instructions231Table 11-16: MIPS16 Special Instructions232Table 11-17: MIPS16 Multiply and Divide Instructions232Table 11-18: MIPS16 Jump and Branch Instructions232                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                           |     |

| Table 11-16: MIPS16 Special Instructions.232Table 11-17: MIPS16 Multiply and Divide Instructions.232Table 11-18: MIPS16 Jump and Branch Instructions.232                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Table 11-14: MIPS16 ALU Immediate Instructions                            | 231 |

| Table 11-17: MIPS16 Multiply and Divide Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Table 11-15: MIPS16 Arithmetic Two or Three Operand Register Instructions | 231 |

| Table 11-18: MIPS16 Jump and Branch Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Table 11-16: MIPS16 Special Instructions                                  | 232 |

| Table 11-18: MIPS16 Jump and Branch Instructions232Table 11-19: MIPS16 Shift Instructions233Table A-1: Revision History234                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Table 11-17: MIPS16 Multiply and Divide Instructions                      | 232 |

| Table 11-19: MIPS16 Shift Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Table 11-18: MIPS16 Jump and Branch Instructions                          | 232 |

| Table A-1: Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Table 11-19: MIPS16 Shift Instructions.                                   | 233 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Table A-1: Revision History                                               | 234 |

### Introduction to the MIPS32<sup>TM</sup> M4K<sup>TM</sup> Processor Core

The MIPS32<sup>TM</sup> M4K<sup>TM</sup> core from MIPS Technologies is a high-performance, low-power, 32-bit MIPS RISC processor core intended for custom system-on-silicon applications. The core is designed for semiconductor manufacturing companies, ASIC developers, and system OEMs who want to rapidly integrate their own custom logic and peripherals with a high-performance RISC processor. A M4K core is fully synthesizable to allow maximum flexibility; it is highly portable across processes and can easily be integrated into full system-on-silicon designs. This allows developers to focus their attention on end-user specific characteristics of their product.

The M4K core is ideally positioned to support new products for emerging segments of the routing, network access, network storage, residential gateway, and smart mobile device markets. It is especially well-suited for applications where high performance density is critical, especially those requiring multiple processor cores on a single chip.

The core implements the MIPS32 Release 2 Instruction Set Architecture (ISA), and may optionally support the MIPS16e Application Specific Extension (ASE) for code compression. The MMU consists of a simple Fixed Mapping Translation (FMT) mechanism, for applications that do not require the full capabilities of a Translation Lookaside Buffer- (TLB-) based MMU available on other MIPS cores.

The M4K core is cacheless; in lieu of caches, it includes a simple interface to SRAM-style devices. This interface may be configured for independent instruction and data devices or combined into a unified interface. The SRAM interface allows deterministic latency to memory, while still maintaining high performance.

The core includes one of two different Multiply/Divide Unit (MDU) implementations, selectable at build-time, allowing the user to trade off performance and area for integer multiply and divide operations. The high-performance MDU option implements single cycle multiply and multiply-accumulate (MAC) instructions, which enable DSP algorithms to be performed efficiently. It allows 32-bit x 16-bit MAC instructions to be issued every cycle, while a 32-bit x 32-bit MAC instruction can be issued every other cycle. The area-efficient MDU option handles multiplies with a one-bit-per-clock iterative algorithm.

The basic Enhanced JTAG (EJTAG) features provide CPU run control with stop, single stepping and re-start, and with software breakpoints through the SDBBP instruction. Additional EJTAG features - instruction and data virtual address hardware breakpoints, connection to an external EJTAG probe through the Test Access Port (TAP), and PC/Data tracing, may optionally be included.

.The rest of this chapter provides an overview of the MIPS32 M4K processor core and consists of the following sections:

- Section 1.1, "Features"

- Section 1.2, "M4KTM Core Block Diagram"

### 1.1 Features

- 5-stage pipeline

- 32-bit Address and Data Paths

- MIPS32-Compatible Instruction Set

- Multiply-add and multiply-subtract instructions (MADD, MADDU, MSUB, MSUBU)

- Targeted multiply instruction (MUL)

- Zero and one detect instructions (CLZ, CLO)

- Wait instruction (WAIT)

- Conditional move instructions (MOVZ, MOVN)

- Prefetch instruction (PREF)

- MIPS32 Enhanced Architecture (Release 2) Features

- Vectored interrupts and support for an external interrupt controller

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow sets

- Bit field manipulation instructions

- MIPS16e Application Specific Extension

- 16 bit encodings of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- Data type conversion instructions (ZEB, SEB, ZEH, SEH)

- Compact jumps (JRC, JALRC)

- Stack frame set-up and tear down "macro" instructions (SAVE and RESTORE)

- Programmable Memory Management Unit

- Simple Fixed Mapping Translation (FMT)

- Address spaces mapped using register bits

- Simple SRAM-Style Interface

- Cacheless operation enables deterministic response and reduces size

- 32-bit address and data; input byte enables enable simple connection to narrower devices

- Single or multi-cycle latencies

- Configuration option for dual or unified instruction/data interfaces

- Redirection mechanism on dual I/D interfaces permits D-side references to be handled by I-side

- Transactions can be aborted

- Multi-Core Support

- External lock indication enables multi-processor semaphores based on LL/SC instructions

- External sync indication allows memory ordering

- Debug support includes cross-core triggers

- CorExtend<sup>TM</sup> User Defined Instruction capability (access to this feature is available in the M4K Pro<sup>TM</sup> cores and requires a separate license)

- Optional support for the CorExtend feature allows users to define and add instructions to the core (as a build-time option)

- Single or multi-cycle instructions

- Source operations from register, immediate field, or local state

- Destination to a register or local state

- Full featured Coprocessor 2 Interface